In part 1, I spent a good deal of time explaining how to make Gerber files from the bitmap foils found on Grant Searle’s site. In this part, I’ll go a little deeper into a problem that seems to plague many ZX80 replicas: inverted characters not showing up correctly.

First of all, grab this PDF: http://searle.x10host.com/zx80/zx80circuitAnnotated.pdf

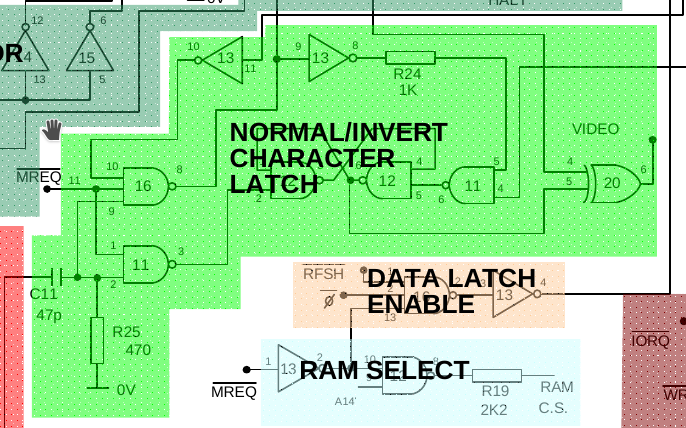

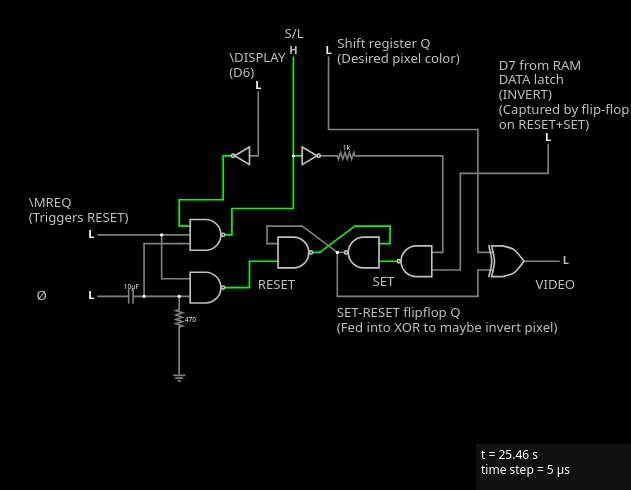

We’ll mostly be looking at this green part in the middle:

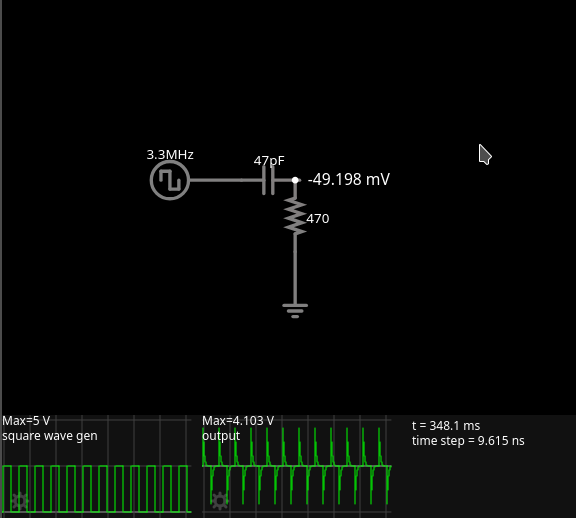

C11 is unusual in a digital circuit. Capacitors don’t pass DC. But digital circuits are DC, in a way. C11, together with R25, takes the clock signal (3.25 MHz) and mangles it.

Edit 2025-10-29: Ben Eater uses and explains this circuit in this video: https://www.youtube.com/watch?v=YW-_GkUguMM&t=624s.

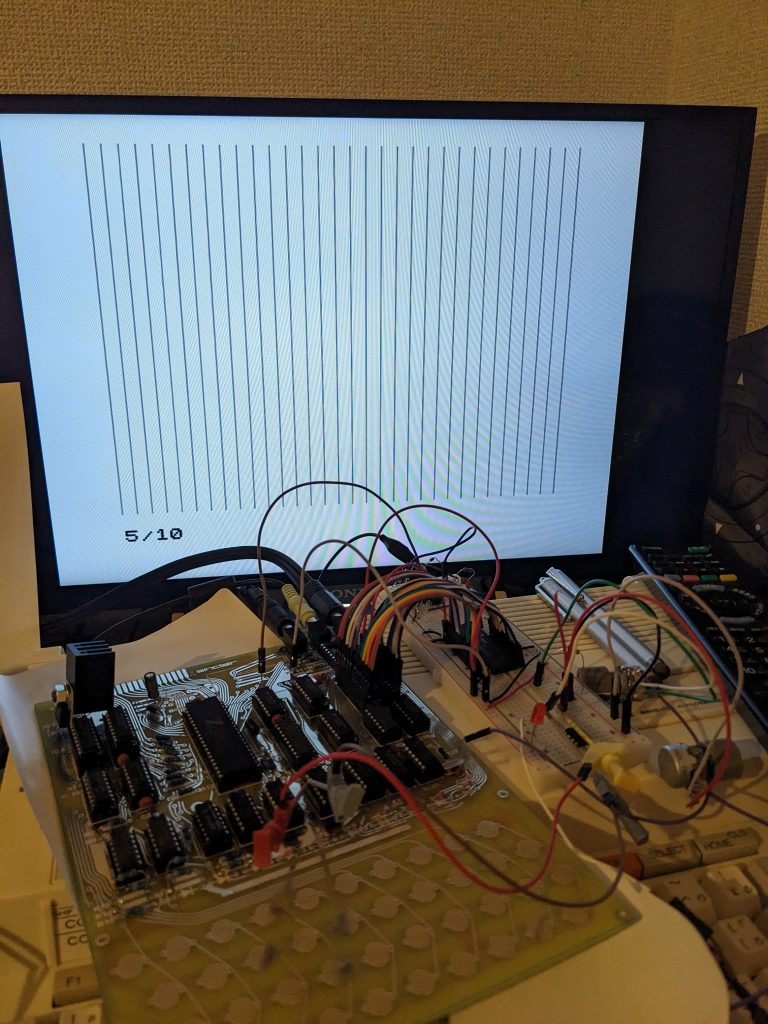

In this simulation, we turn a nice 0V-5V square wave into a spiky thing with -4.103V lows and 4.103V highs. And we send this curious signal into two 74LS logic chips, IC11 (74LS00) and IC16 (74LS10). When we look at this signal on an oscilloscope, we see a very low signal (not anywhere near 4.103V), more like -1.4V to 1.4V. Reality is probably somewhere in between. I had Texas Instruments SN74LS00N (from 2019 I think) and SN74LS10N (older markings, not sure what year) chips, and the 74LS10 one was able to see the peaks and interpret them as a logic HIGH. The 74LS00, on the other hand, never interpreted the peaks as a logic HIGH. This produced a picture where inverted characters only had the first column inverted.

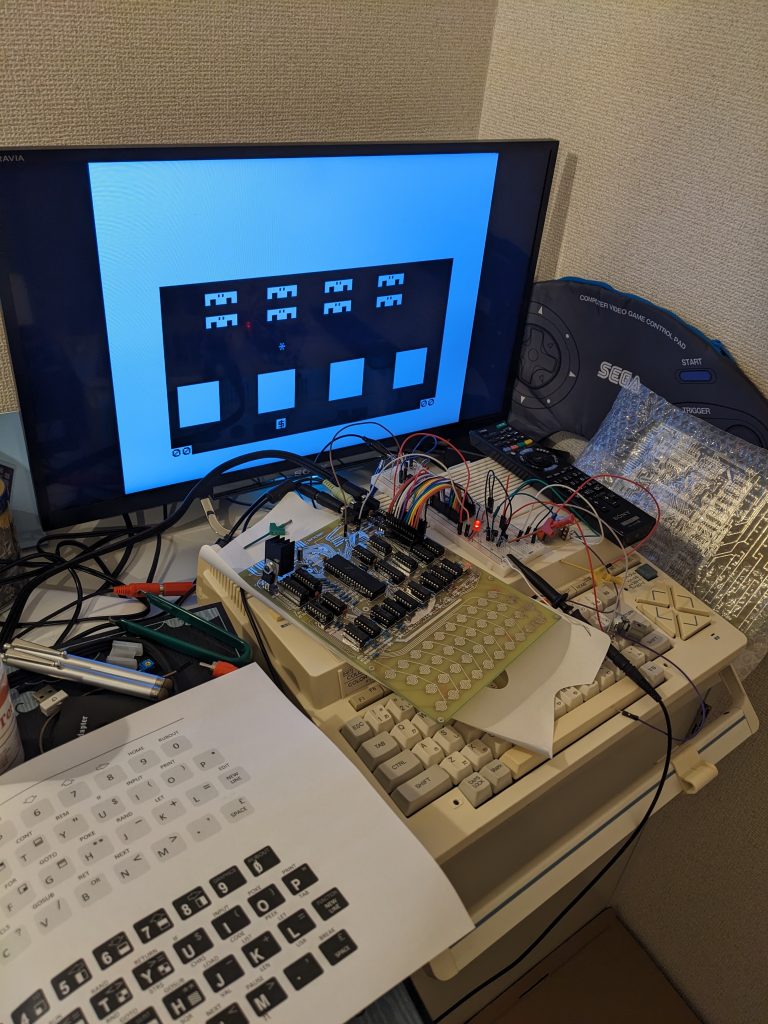

I fixed this problem by buying another 74LS00. I bought one from Hitachi (now Renesas), called HD74LS00P.

Looking around the internet, some people change the capacitor, some change the resistor, some change both, some use different resistors/capacitors pairs on IC11 and IC16. I tried various things but unfortunately this didn’t work for my 74LS00. I believe the simplest solution would be to just get different 74LS00s and 74LS10s from several vendors and trying them out. And if that takes you nowhere, you could maybe try and use a couple transistors to rectify and amplify the signal. (It’s a rather fast signal so that may make it harder than just using a simple common-emitter configuration where the transistor is driven into saturation millions of times per second.)

So what is this RC filter good for anyway?

Let’s have a look at this simulation, which includes the entire “NORMAL/INVERT CHARACTER LATCH” logic:

We have an S-R flipflop implemented using two NAND gates. This flip-flop’s job is to remember the state of D7 (which only briefly remains on the data bus) for 8 pixel clock (6.5 MHz) cycles (the abovementioned 3.25 MHz clock is half the pixel clock). If we didn’t do this, only the first column of each inverted character would be inverted.

How does it do this? For the most part, it’s explained on Grant Searle’s site. Have a look at this extract, though it’s mostly concerned with IC16’s job.

At the very end of the opcode execution (actually, the very start of the next opcode), the load pin on the register is very briefly (via a capacitor) pulsed low, to load whatever is being output on the data bus (from the ROM) into the shift register. The pulse is activated by a positive clock transition. This is only active when /MREQ is high. As you can see from the oscilloscope traces, the only time a positive transition occurs when /MREQ is high is at the start of the T1 state. A further blocking signal (into pin 10 of IC 16) ensures that the trigger pulses only occur when a character has been loaded (ie. when the NOP circuitry has been activated). This ensures that no data is loaded into the shift register at other times during the display.

The data that has been loaded is is then streamed one bit at a time (highest bit first) to the output (via the XOR IC 20, to invert if needed) and then passed directly to the TV modulator to convert the 0 and 1 levels into dark/light bits on the screen.

http://searle.x10host.com/zx80/zx80ScopePics.html

I think it might help to break things down a little further. First of all:

IC11 inputs: mangled clock, \MREQ

IC16 inputs: mangled clock, \MREQ, \DISPLAY (D6)

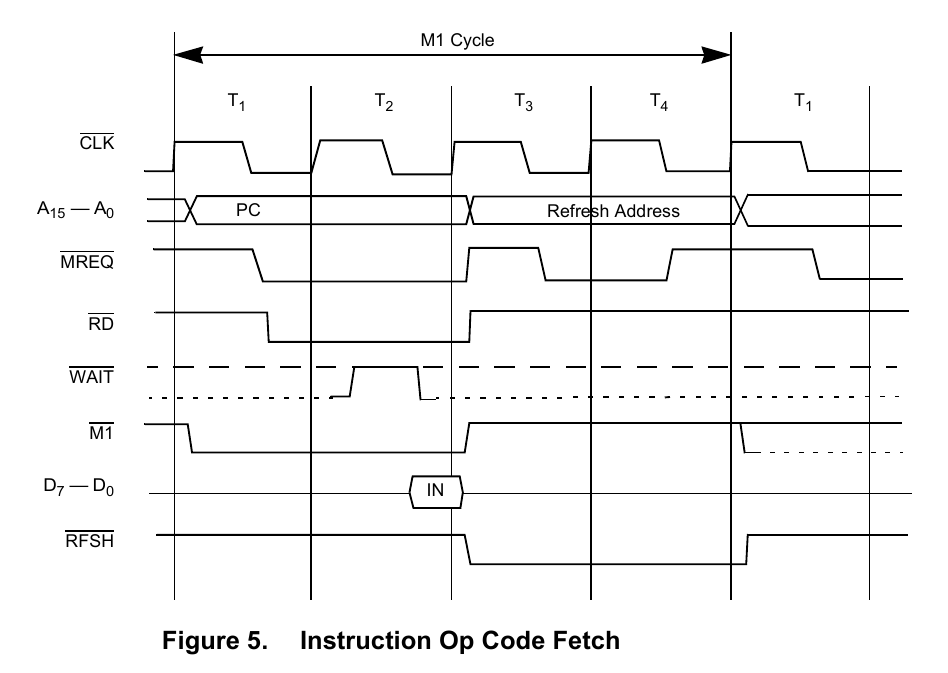

We want the S-R latch to be reset and set to the correct inversion state at the start of every character. On the ZX80 computer, one character is output by executing a NOP (while in \DISPLAY mode). On the Z80 CPU, a NOP is executed in 4 CPU cycles. The pixel clock is twice that speed, so we output 8 pixels in that time. Let’s look at the Z80 CPU’s NOP instruction timings:

We see our \MREQ in the third row. We see it’s already high when entering T1. It also goes high again in T3 and later in T4. But if our flip-flop is reset every time we get a high MREQ and a high clock, that would mean our flip-flop gets reset three times per character! Well, that’s where the RC circuit comes into play:

On one side of the capacitor, we have the CLK signal. On the other side of the capacitor, we see a really spiky signal that just goes up for a split microsecond and goes down again, and stays down (or goes down further than required, but that’s… okay). In other words, C11 and R25 implement this bit: “The pulse is activated by a positive clock transition.“

Such cheapskates. ;)